## 論理回路

論理演算を行うための電子回路

コンピュータはデジタルの世界です。数値を二進法の 0と1で表すのですが、コンピュータの内部ではそれを OVと5Vのように、電圧がない・あるという状態で区別 します。この仕組みを、半導体を組み合わせた電子回路 である論理回路で実現しています。では、その論理回路 にはどのようなものがあるのかを見てみましょう。

この論理回路の最も基本となるものがAND(論理 積)、OR (論理和)、NOT (論理否定) の3種類で、この 3つの組み合わせで、すべての論理回路を構成すること ができます。

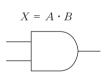

#### AND(論理積)

AND は複数の入力がすべて 1 のときのみ 1 を出力し、 入力信号に〇が含まれていれば出力は〇になります。

図1 ANDの論理式と図記号

表1 ANDの真理値表

(2入力の場合)

| (= ) () () () |     |     |  |  |

|---------------|-----|-----|--|--|

| 入力A           | 入力B | 出力X |  |  |

| 0             | 0   | 0   |  |  |

| 0             | 1   | 0   |  |  |

| 1             | 0   | 0   |  |  |

| 1             | 1   | 1   |  |  |

| 入力A | 入力B | 出力X |  |

|-----|-----|-----|--|

| 0   | 0   | 0   |  |

| 0   | 1   | 0   |  |

| 1   | 0   | 0   |  |

| 1   | 1   | 1   |  |

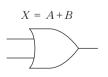

## OR(論理和)

ORは複数の入力がすべてOのときのみOを出力し、 入力信号に1が含まれていれば出力は1になります。

図2 ORの論理式と図記号

#### 表2 ORの真理値表 (2入力の場合)

| 入力A | 入力B | 出力X |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 1   |

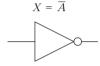

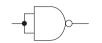

#### NOT(論理否定)

NOTは入力がOのときに1を出力し、入力が1のと きに0を出力します。

図3 NOTの論理式と図記号

| 表3 NOTの真理値表 |     |  |  |  |

|-------------|-----|--|--|--|

| 入力A         | 出力X |  |  |  |

| 0           | 1   |  |  |  |

| -1          | 0   |  |  |  |

#### XOR(排他的論理和)

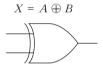

論理回路の基本は AND、OR、NOT ですが、これ以外 にもXOR (eXclusive OR: 排他的論理和) というもの もあります。XORは、2つの入力が異なっている場合は 1を出力し、入力信号が同じ場合は0を出力します。

図4 XORの論理式と図記号

| 表4 XORの真理値表 |     |     |     |  |

|-------------|-----|-----|-----|--|

|             | 入力A | 入力B | 出力X |  |

|             | 0   | 0   | 0   |  |

| -           | 0   | 1   | 1   |  |

|             | 1   | 0   | 1   |  |

| 2등          | 1   | 1   | 0   |  |

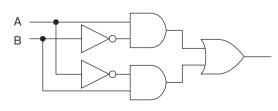

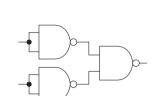

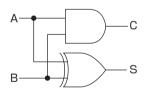

もちろん、このXORも、AND、OR、NOTの組み合 わせで作ることはできます。しかしその場合は、図5の ような複雑な回路になります。XORを使えば簡単な回 路で済みます。

図5 AND、OR、NOTで構成したXOR回路

### NANDとNORの 論理の完全性

AND, OR, NOT, XORのほかに、 比較的よく使われるものとして NANDやNORがあります。NAND

表5 NANDの真 理值表

理值表

0

1 0

表6 NORの真

図7 NORの図記号

は否定論理積、NORは否定論理和の ことで、それぞれ、ANDとORの結果 を否定したものになっています(図 6、図7)。

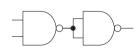

実は、このNAND(またはNOR)

図8 NANDで構成したNOT回路

図9 NANDで構成したAND回路

は、それだけであらゆる論理回路を構

成することができます(図8~図10)。

このように、どんな論理回路でも、

NAND (またはNOR) だけで構成で

きることを、NAND論理の完全性

(NOR論理の完全性)と言います。

図10 NANDで構成したOR回路

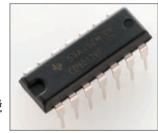

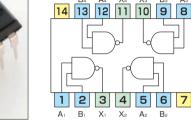

図11 NAND回路 のICチップ とピン配列

# 半加算器と全加算器

1 0 0

1 1 0

二進法1桁同士の加算は表7のよう になります。

表7 二進法1 桁同士の加算

| A+B |   | 桁上げC | その桁の答え<br>S |  |

|-----|---|------|-------------|--|

| 0   | 0 | 0    | 0           |  |

| 0   | 1 | 0    | 1           |  |

| 1   | 0 | 0    | 1           |  |

| 1   | 1 | 1    | 0           |  |

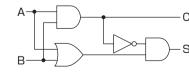

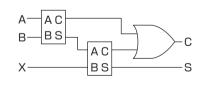

このとき、その桁の答えをS、桁上 げをCとすると、SとCは図12の回 路で求めることができます。

図12 半加算器(その1)

このような加算を行なう回路を半 加算器と言います。

ここで表7を見てみると、入力A、 Bに対して、SはXOR、CはANDに なっているのがわかります。従って、 図12の半加算器は、図13のように 書くこともできます。

図13 半加算器 (その2)

半加算器は下からの桁上げを考慮し ていません。下からの桁上げも考慮し た加算器は、全加算器と言います。下 からの桁上げ入力をXとすると、表8、 図14のように表すことができます。

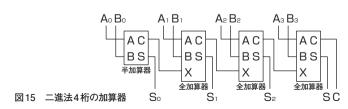

下1桁に半加算器、その上位桁に全

加算器を接続すると、任意の桁の加算 器を作ることができます(図15)。

表8 下からの桁上げを考慮した加算

| A+B |   | 下からの<br>桁上げX | 桁上げC | その桁の<br>答え S |

|-----|---|--------------|------|--------------|

| 0   | 0 | 0            | 0    | 0            |

| 0   | 0 | 1            | 0    | 1            |

| 0   | 1 | 0            | 0    | 1            |

| 0   | 1 | 1            | 1    | 0            |

| 1   | 0 | 0            | 0    | 1            |

| 1   | 0 | 1            | 1    | 0            |

| 1   | 1 | 0            | 1    | 0            |

| 1   | 1 | 1            | 1    | 1            |

図14 全加算器